FPGA三分频练习

2025-07-11

33

0

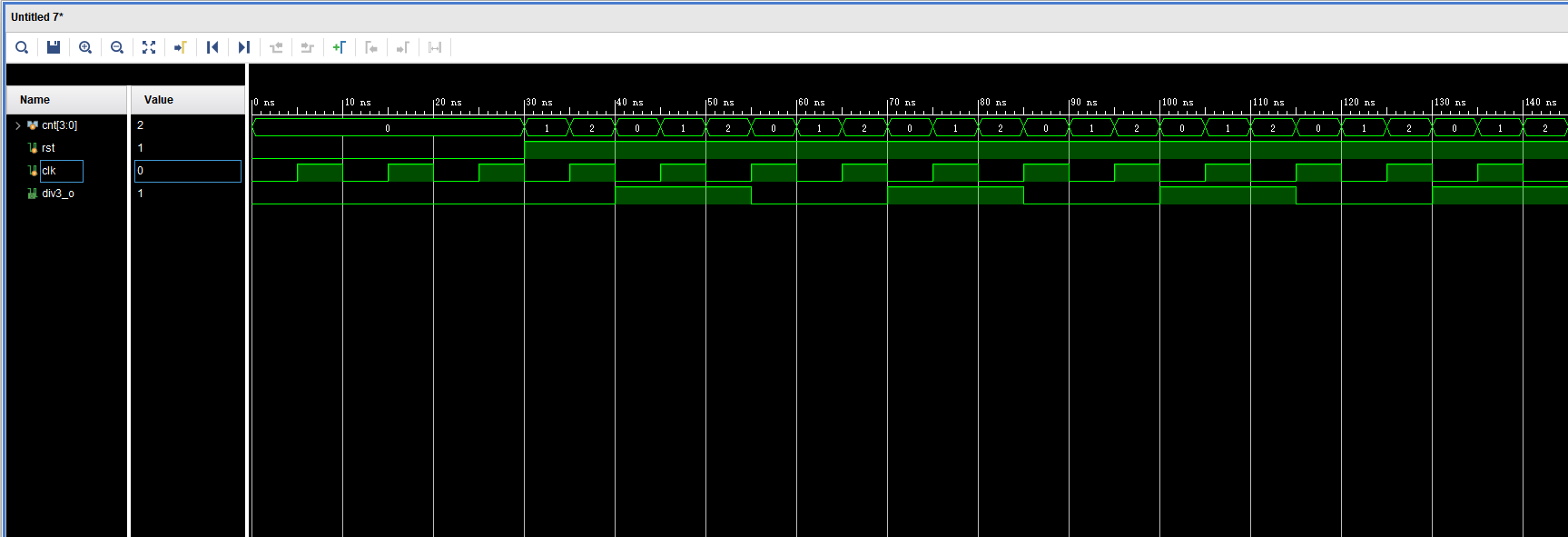

三分频练习指的是将时钟三分频,比如原来时钟周期为10ns,现在需要的是30ns。由于不是2的整数倍,故需要计数下降沿和上升沿。

代码如下:

`timescale 1ns / 1ps

module div3(input clk,input rst,output div3_o);

reg[3:0] cnt;

reg rout;

always@(posedge clk or negedge clk)

begin

if(!rst)

begin

cnt <=0;

end

else if(cnt==2)

cnt <= 0;

else

cnt <= cnt+1;

end

always@(posedge clk or negedge clk)

begin

if (!rst)

rout<=0;

else if(cnt==2)

rout <= ~rout;

else

rout<= rout;

end

assign div3_o = rout;

endmodule

仿真代码:

`timescale 1ns / 1ps

module div3_tb( );

reg clk;

reg rst;

wire div3_o;

initial begin

clk = 0;

rst = 0;

#30

rst = 1;

end

div3 div3_inst(

.clk(clk),

.rst(rst),

.div3_o(div3_o)

);

always #5 clk =~clk;

endmodule

仿真结果如下:

FPGA入门练习

FPGA入门练习