AXI4-Stream、AXI4和AXI4-Lite的区别及共存性

2025-07-19

148

0

| 特性 | AXI4-Stream | AXI4 | AXI4-Lite |

|---|---|---|---|

| 设计目的 | 高速流数据传输 | 高性能内存映射接口 | 简单寄存器访问 |

| 通道结构 | 单向流数据 | 5通道(读/写地址、数据、响应) | 简化版AXI4(无突发) |

| 地址机制 | 无地址 | 带地址的突发传输 | 单次地址传输 |

| 突发传输 | 连续流(无明确突发) | 支持(最多256次突发) | 不支持 |

| 典型应用 | 视频流、DMA传输 | 处理器与内存连接 | 控制寄存器访问 |

| 复杂性 | 中等 | 高 | 低 |

- 协议独立性:这三种协议设计用于不同场景,没有根本性冲突

- 应用场景互补:

- AXI4用于高性能内存访问,主要用于访问内存映射的设备,如存储器和I/O设备,适合大量数据传输。

- AXI4-Lite用于寄存器配置

- AXI4-Stream用于数据流传输,主要用于流式数据传输,适用于连续数据流场景,如视频处理和高速数据传输。

- FPGA/SoC实现:现代FPGA和SoC通常支持多种AXI接口共存

典型共存应用示例

视频处理系统:

- AXI4-Lite:配置视频处理IP核的寄存器

- AXI4:访问DDR内存

- AXI4-Stream:传输视频数据流

网络加速器:

- AXI4-Lite:控制寄存器配置

- AXI4:与主机内存交互

- AXI4-Stream:处理网络数据包

在实际设计中,这三种协议经常被组合使用以满足不同的数据传输和控制需求。

ZYNQ7035 PICE IP核LOCAL端的AXI4

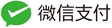

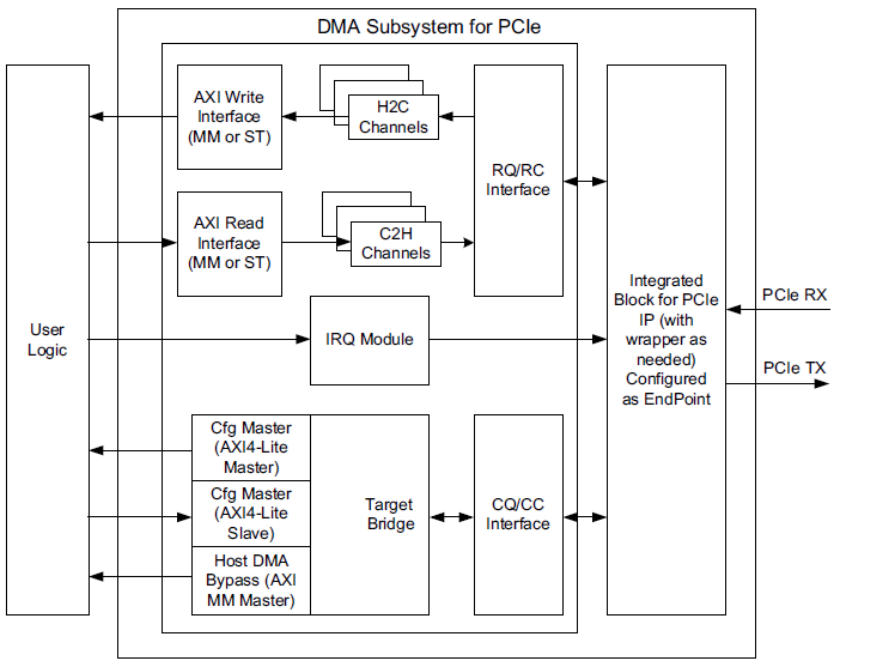

Xilinx 提供的DMASubsystem for PCIExpressIP是一个高性能,可配置的适用于PCIE2.0, PCIE3.0 的SG 模式 DMA,提供用户可选择的 AXI4 接口或者 AXI4-Stream接口。

- 一般情况下配置成 AXI4 接口可以加入到系统总线互联,适用于大数据量异步传输,通常情况都会使用到 DDR

- AXI4-Stream 接口适用于低延迟数据流传输。

XDMA 是SGDMA,并非Block DMA, SG 模式下,主机会把要传输的数据组成链表的形式,然后将链表首地址通过BAR 传送给XDMA, XDMA 会根据链表结构首地址依次完成链表所指定的传输任务。

- AXI4、 AXI4-Stream,必须选择其中一个,用来数据传输

- AXI4-Lite Master,可选,用来实现PCIE BAR 地址到 AXI4-Lite 寄存器地址的映射,可用来读写用户逻辑寄存器

- AXI4-Lite Slave,可选,用来将XDMA 内部寄存器开放给用户逻辑,用户逻辑可以通过此接口访问 XDMA内部寄存器,不会映射到BAR

- AXI4 Bypass 接口,可选,用来实现PCIE 直通用户逻辑访问,可用于低延迟数据传输

在配置IP时,AXI(memory mapped)和AXI Steam选其一,不过一般选择的是AXI;AXI-LITE是可选择。

总线及时序

总线及时序