PCIe技术架构深度解析

2025-08-06

100

0

核心架构特性

PCIe采用四大创新设计实现高速互联:

- 高速串行通信:突破传统并行总线限制

- 点对点连接:每个设备独享带宽通道

- 交换式架构:通过智能交换机管理多路连接

- 数据包化协议:采用网络化传输机制

注:链路协商与训练过程对系统效能至关重要,动态链路活动的捕获与分析是调试的核心环节。

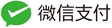

PCIe分层架构详解

| 架构层级 | 核心功能 | 技术细节 |

|---|---|---|

| 应用层 | • 承载上层协议(NVMe/Ethernet等)<br>• 不定义具体载荷内容 | 作为传输管道,仅规范数据传输方式 |

| 事务层 | • 设备链路配置<br>• 内存读写控制<br>• 消息传递与错误报告 | 包含配置寄存器空间,支持MemRd/MemWr/IORd/IOWr等TLP包类型 |

| 数据链路层 | • 数据完整性保障<br>• 流量控制(ACK/NAK)<br>• 低功耗状态管理 | 采用CRC错误检测,支持L0s/L1等节能状态切换 |

| 物理层 | • 电气子层:模拟信号处理<br>• 逻辑子层:链路训练与状态机控制 | 包含均衡器(Equalizer),支持128b/130b编码(PCIe 3.0+) |

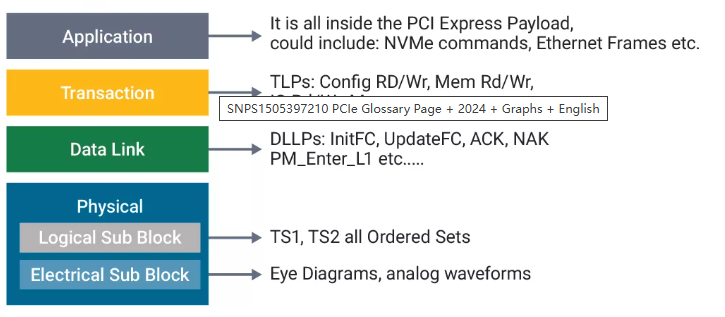

链路建立与数据传输

全双工通信架构:

- 每个端口包含独立TX/RX通道

- 采用差分信号传输(2.5GHz~32GHz)

端到端传输流程:

graph LR A[设备驱动生成TLP] --> B(事务层封装) B --> C(数据链路层添加序列号/CRC) C --> D(物理层信号调制) D --> E[(通道传输)] E --> F[对端物理层解调] F --> G(数据链路层校验) G --> H(事务层解包)关键创新技术:

- 链路训练(Link Training):通过TS1/TS2有序集协商参数

- 弹性缓冲(Elastic Buffer):解决时钟容差问题

- 去加重(De-emphasis):补偿高频信号衰减

PCIE百科

PCIE百科