PCIe学习(七)

5 电源管理

PCIe的电源管理是一个系统性的话题。我们今天来一探究竟。

5.1 链路状态电源管理

首先就要先来提一提ACPI (Advanced Configuration and Power Interface)。ACPI旨在为操作系统和应用程序提供所有芯片电源管理的接口。

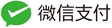

ACPI定义了系统电源管理状态:

Ø G0/S0:工作状态。系统处于火力全开的工作状态。

Ø G1:睡眠状态。此状态下系统功耗较小,返回工作状态的时间取决于下面几个子状态

² S1:高速缓存被清空,CPU挂起

² S2:与S1类似,但是CPU电源被关断

² S3:也称为“挂起到RAM(Suspend to RAM)”或者“待机(Standby)”,系统上下文被保存到内存

² S4:也称为“挂起到硬盘(Suspend to Disk)”或者“休眠(Hibernate)”,系统上下文被保存到硬盘

Ø G2/S5:软件关机。此状态下系统功耗最小,系统当前状态信息不被保留,需要完全重新启动才能返回工作状态。绝大部分硬件设备处于断电状态,少数硬件有一些电源可用于唤醒,例如按下系统上的电源按钮。

ØG3:机械关机。系统的电源被完全切断。

#

ACPI也定了设备电源状态:

Ø D0:设备的全部供电打开,处于完全运行的状态。

Ø D1:低功耗状态(比D0低),设备上下文可能会丢失,也可能不会丢失。

Ø D2:比D1更低的功耗状态,但会导致更长的恢复延迟,并可能导致设备丢失上下文。

Ø D3:设备已做好断电准备,设备的上下文都可能丢失。恢复时间将比D2更长,但在这种状态下可以正常断开设备电源。

其中D1和D2不是强制性的,设备可以根据具体情况选择是否实现这两个状态。

#

再来看看PCIe协议做了哪些定义。

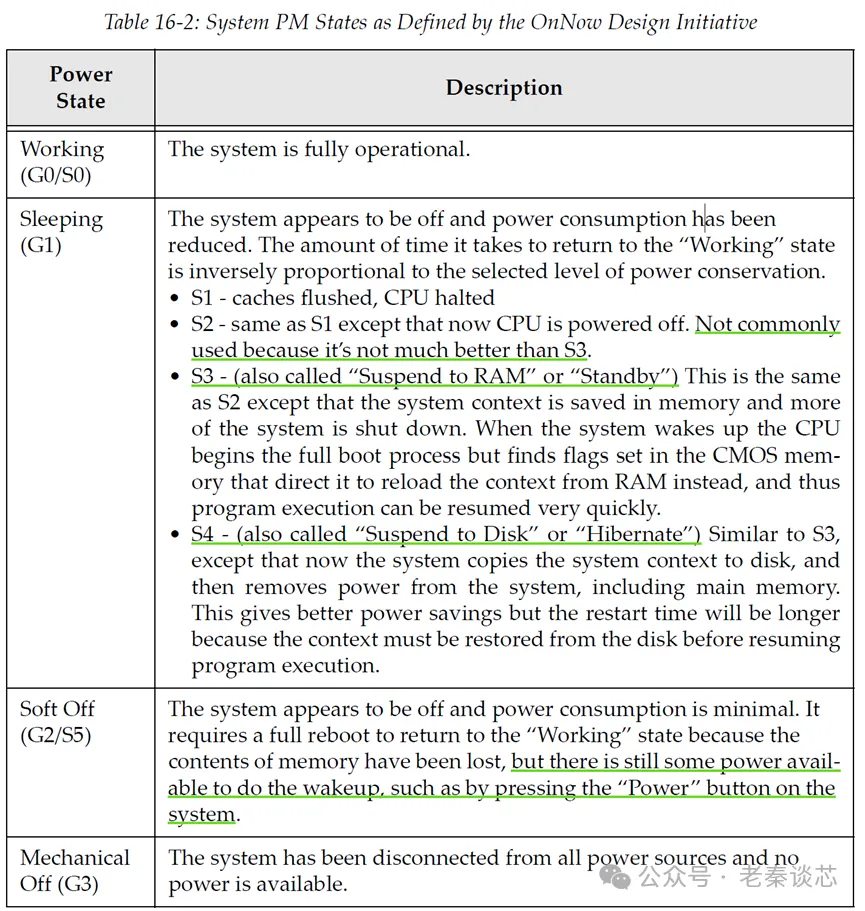

首先,PCIe协议中定义了链路电源管理状态:

Ø L0:所有PCIe事务和操作都启用

Ø L0s:Standby模式,恢复延迟低,功耗低

Ø L1:可以分为几个子状态L1.0,L1.1和L1.2

Ø L2/L3 Ready:L2或L3的临时状态,L2/L3 Ready是一种伪状态(pseudo-state)

Ø L2:辅助供电链路状态

Ø L3:链路关闭状态

Ø LDn:L0之前的过渡链路断开伪状态

下图是PCIe链路电源管理状态转换图。需要注意的是,L0s,L1,L2,L3这些状态之间没有直接转换的关系,千万不要想当然的认为存在L0->L1->L2->L3这种顺序关系。理解下面这张图是理解PCIe链路电源状态的关键。

#

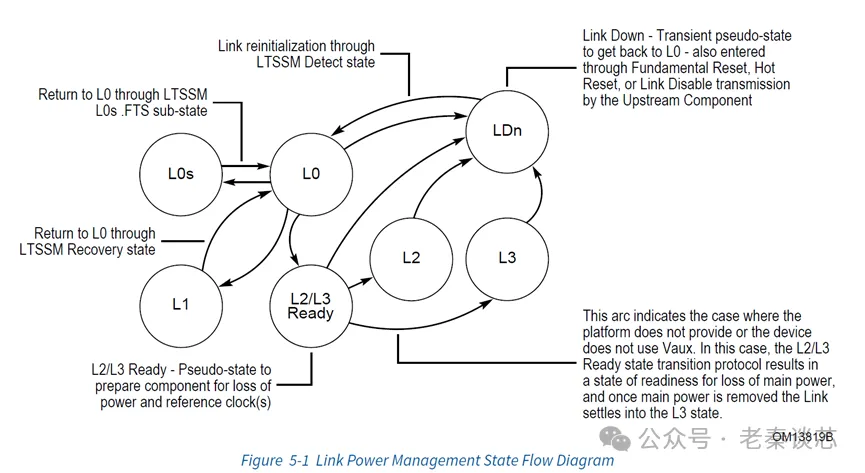

然后,PCIe协议中定义了设备状态:

Ø D0:这是PCIe设备必须支持的状态,包含两个子状态

² D0uninitialized:Function完成基本复位后,进入此状态。通常,寄存器在此状态下恢复为默认值。此时,Function只能响应配置请求,不能发起事务,也不能处理接收到的Memory或者IO事务。

² D0active:当Function被系统软件正确配置后,进入此状态

Ø D1:也称为轻度睡眠状态(Light Sleep),该状态是可选的,设备不是必须支持。当Function进入D1状态时,链路进入L1状态。此时设备只可以接收配置请求和消息请求

Ø D2:也称为深度睡眠状态(Deep Sleep),该状态是可选的,设备不是必须支持。在进入此状态前,软件需要确保所有的Non-Posted请求都得到了Completion。设备进入D2状态后,对应的链路进入L1状态。此时设备只可以接收配置请求和消息请求

Ø D3:又称为全关(Full-Off)状态。D3状态是设备必须支持的状态,包含两个子状态

Ø D3hot:当设备进入D3hot状态,表明该设备的电源尚未切断,链路进入L1状态

Ø D3cold:当设备进入D3cold状态,则表明设备的电源已被切断,如有Vaux存在,则链路进入L2状态,否则进入L3状态

PCIe的设备电源状态是与ACPI设备电源状态对应的,而且在D0和D3设备状态中又细分了子状态。

PCIe链路电源状态与设备电源状态的对应关系见下图:

总结一下,上游组件的设备电源状态不能比下游组件更激进,比如不允许RC先于EP进入低功耗状态;链路两端设备的电源状态不能比链路电源状态更激进,比如不允许设备进入睡眠状态,而链路处于工作状态。

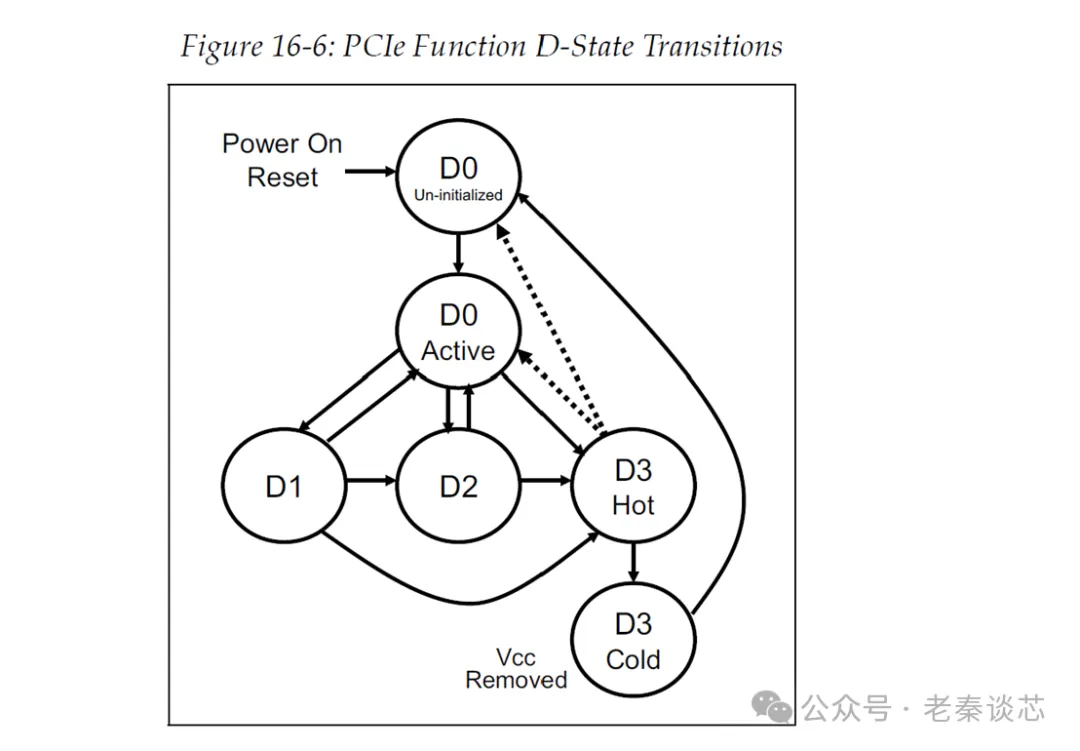

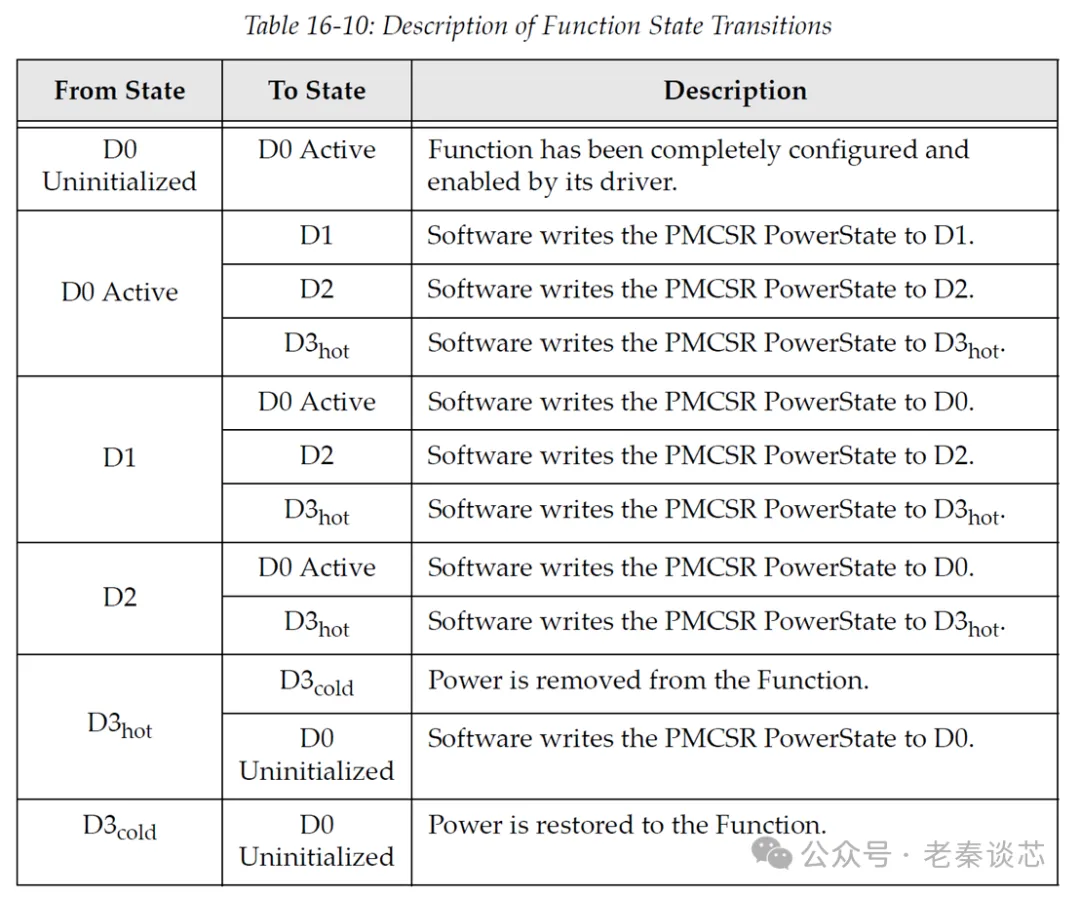

Function的电源状态转换图如下:

系统软件可以通过配置Function的PMCSR寄存器来设置Function的电源状态。

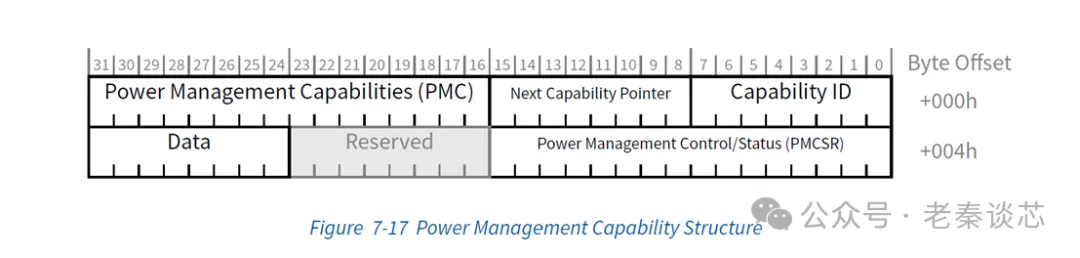

电源管理能力结构

上图中提到的PMCSR寄存器位于电源管理能力结构(Capability Structure)中。

Power Management Capability ID寄存器

PCIe协议为电源管理能力分配的ID是01h。

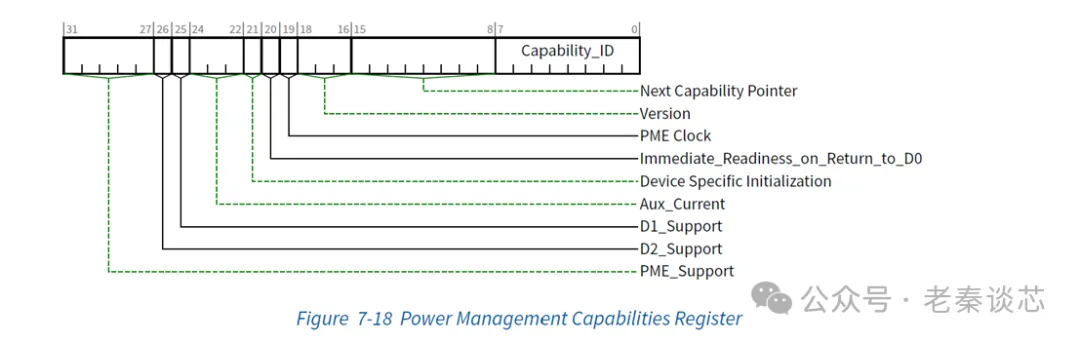

Power Management Capability寄存器

该寄存器位于Capability Structure Header的高16-bit。

各字段含义:

Ø PME Clock:不适用于PCIe

Ø Immediate_Readiness_on_Return_to_D0:1b表示该Function可以在被设置为D0之后立即准备好成功完成有效访问

Ø Device Specific Initialization:指示是否需要对该Function进行特殊初始化。

Ø Aux_Current:报告Function的Vaux辅助电流要求,编码如下表

| Aux_Current[2:0] | Vaux Max. Current Required (mA) |

| 111b | 375 |

| 110b | 320 |

| 101b | 270 |

| 100b | 220 |

| 011b | 160 |

| 010b | 100 |

| 001b | 55 |

| 000b | 0 |

Ø D1_Support:Function是否支持D1状态

Ø D2_Support:Function是否支持D2状态

Ø PME_Support:指示Function可以生成PME或转发PME消息的电源状态,编码如下表:

| PME_Support[4:0] | Function can assert PME |

| XXXX1b | PME can be generated from D0 |

| XXX1Xb | PME can be generated from D0 |

| XX1XXb | PME can be generated from D0 |

| X1XXXb | PME can be generated from D3hot |

| 1XXXXb | PME can be generated from D3cold |

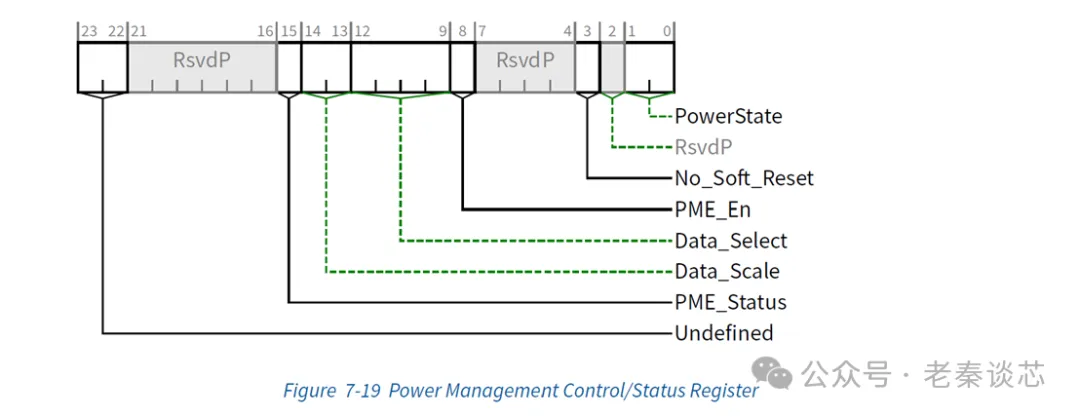

Power Management Control/Status寄存器

各字段含义:

Ø PowerState:既用于确定Function的当前电源状态,又用于将Function设置为新的电源状态,编码如下:

| PowerState[1:0] | Power state of Function |

| 00b | D0 |

| 01b | D1 |

| 10b | D2 |

| 11b | D3hot |

Ø No_Soft_Reset:指示在写入PowerState字段以将Function从D3Hot转换为D0之后Function的状态。

Ø PME_En:该位被设置,表示允许Function产生PME

Ø Data_Select:由于选择要通过Data寄存器和Data_Scale字段报告的数据。

Ø Data_Scale:指示在解释Data寄存器的值时要使用的缩放因子

Ø PME_Status:当Function可以正常产生PME时,设置此位

Ø Undefined:在之前版本用到,Gen 5中不用

Data寄存器

Data寄存器是可选的8-bit只读寄存器,为电源管理能力提供了一种机制,来报告与状态相关的功耗。如果实现Data寄存器,则PMCS寄存器中的Data_Select和Data_Scale字段也要实现,具体的配合关系参见PCIe基本协议。

微信公众号和word有点不兼容,格式有点乱,大家将就看吧~~

【待续】

PCIE学习

PCIE学习